## Final Presentation

# A Reconfigurable SRAM based CMOS PUF with Challenge to Response Pairs

S. Baek, G.H. Yu, J. Kim, C.T. NGO, J.K. Eshraghian and J.P. Hong

Jinay Dagli [20110084] and Neel Shah [20110187]

Department of Electrical Engineering, Indian Institute of Technology Gandhinagar

{jinay.dagli, shah.neel}@iitgn.ac.in

#### **Outline**

- Objective

- Introduction

- Why Physically Unclonable Functions (PUFs)?

- Significance of PUFs

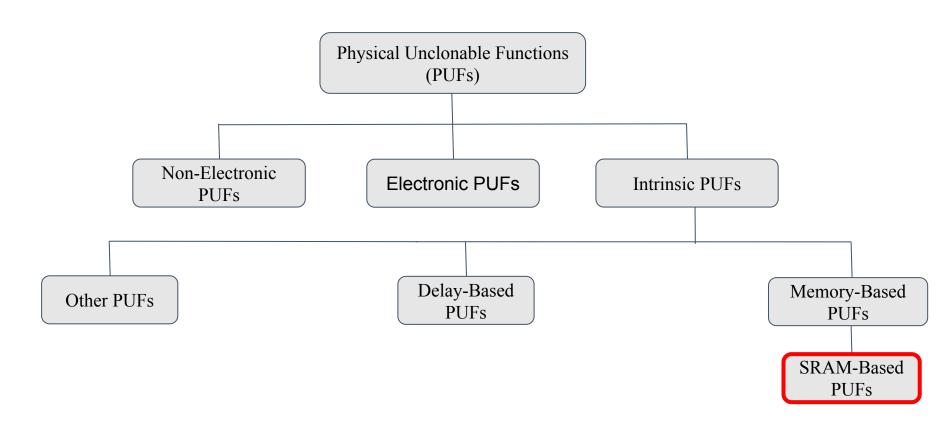

- Classification of PUFs

- Conventional SRAM-based PUF

- Reconfigurable SRAM-based PUF

- Schematic

- Circuit Implementation

- Simulations

- Results

## **Objective**

#### **➤** Implement the Reconfigurable SRAM-PUF Design

The paper by S. Baek et al. proposes reconfigurable SRAM-PUF with multiple CRPs. We had to implement it on 28 nm technology to check the scalability.

#### ➤ Analysis of Randomness in the PUF Design

• Analyze the PUF design in terms of possible number of CRPs, randomness in response bits generated, static power, average dynamic energy etc. by performing various simulations.

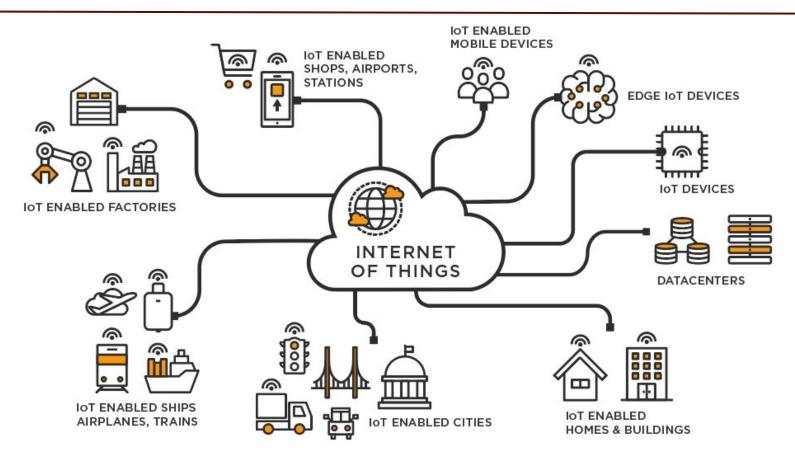

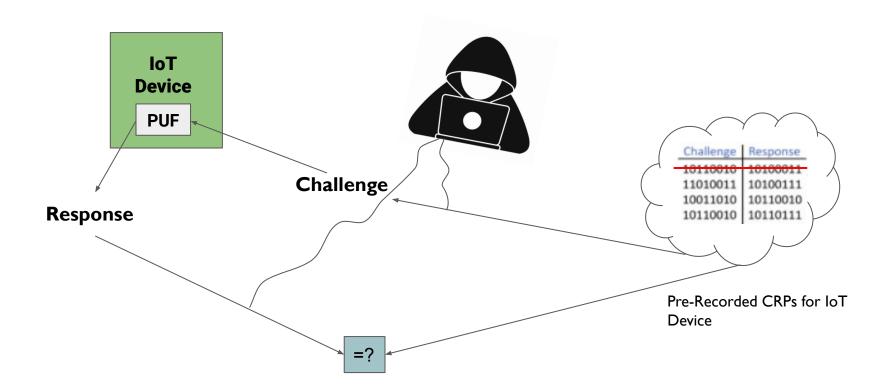

#### Introduction

## **Significance of PUFs**

#### **Classification of PUFs**

#### **Conventional SRAM-based PUF**

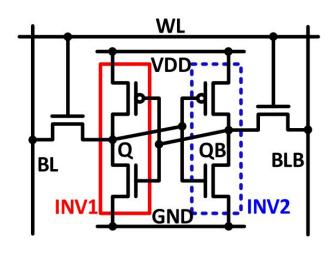

SRAM Cell,  $V_{th}$  differences in the transistors result in the SRAM powering up in either a logic "0" (Q = 0, QB = 1) or logic "1" (Q = 1, QB = 0).

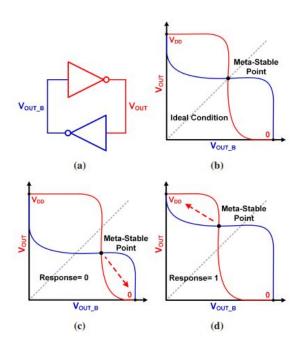

Voltage Transfer Characteristics of Conventional SRAM PUF

## **Reconfigurable SRAM-based PUF**

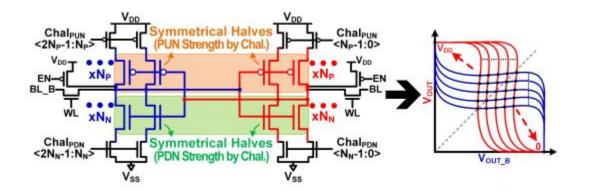

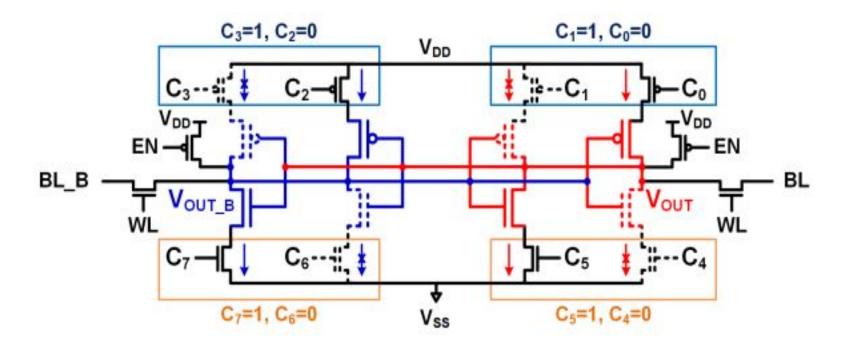

The reconfigurable SRAM cell comprises of multiple cross-coupled inverters with challenge inputs applied to switching transistors to reconfigure the relative strength of the pull-up network (PUN) and pull-down network (PDN).

## Reconfigurable SRAM-based PUF (An Example)

## **Reconfigurable SRAM-PUF (CRP Space Calculation)**

$$N_N$$

(or  $N_P$ ) = No. of NMOS (or PMOS) making up the inverter on each side

$$N_N \text{ (or } N_P) = 1, \text{ No. of } CRPs = 1$$

$$N_N \text{ (or } N_P) = 2$$

, No. of  $CRPs = 2 \times 2 + 1 = 5$

$$N_{N} \text{ (or } N_{P}) = n \text{ (or } p), \text{ No. of CRPs} = {\binom{n}{C_{1}}}^{2} + {\binom{n}{C_{2}}}^{2} + \dots + {\binom{n}{C_{n-1}}}^{2} + {\binom{n}{C_{n}}}^{2} = \sum_{k=1}^{n} {\binom{n}{C_{k}}}^{2}$$

(1)

Bitwidth of challenge in a cell

$$= (2 \times N_N + 2 \times N_P)$$

bits

Assuming

$$N_N = N_P$$

, Bitwidth of challenge  $= (4 \times N_N)$  bits (2)

No. of transistors in a cell

$$= 8 \times N_N + 4$$

(3)

Total No. of CRPs

$$= \left(\sum_{k=1}^{N_N} (^{N_N} C_k)^2\right)^2 \tag{4}$$

Actual value for

$$N_N = N_P = 8$$

, Bitwidth of challenge = 32 bits

Total No. of CRPs

$$= \left(\sum_{k=1}^{8} (^{8}C_{k})^{2}\right)^{2} \approx 1.6 \times 10^{8}$$

(5)

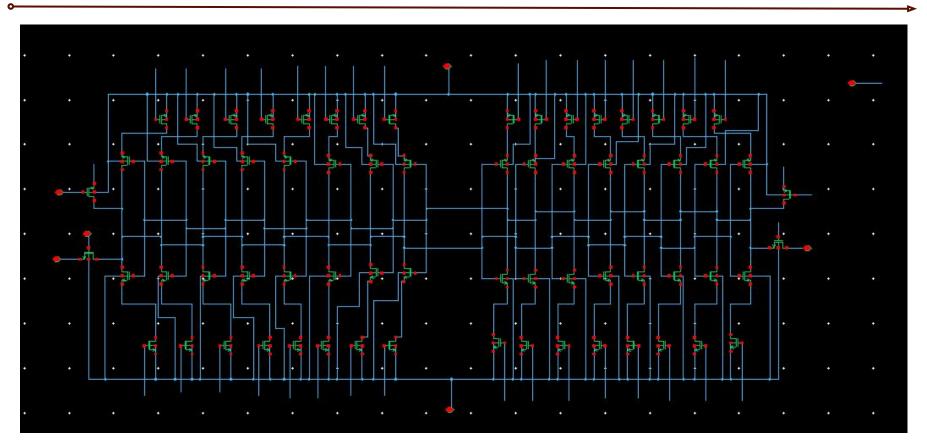

## **Schematic (SRAM-PUF Cell)**

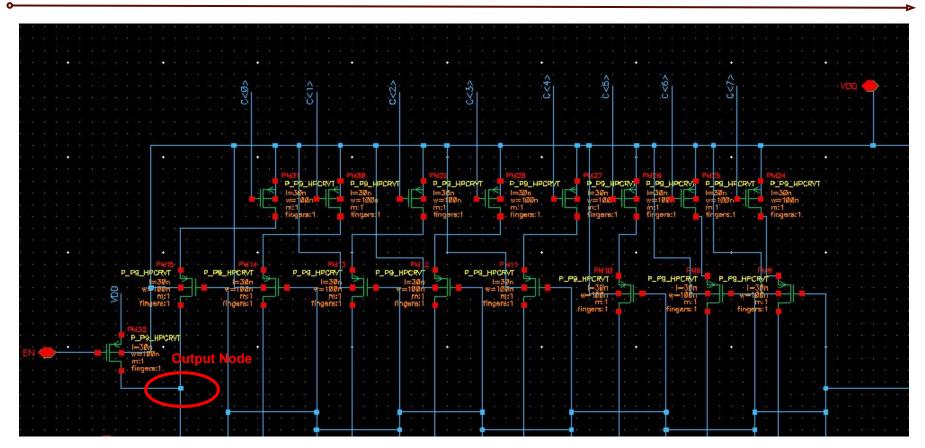

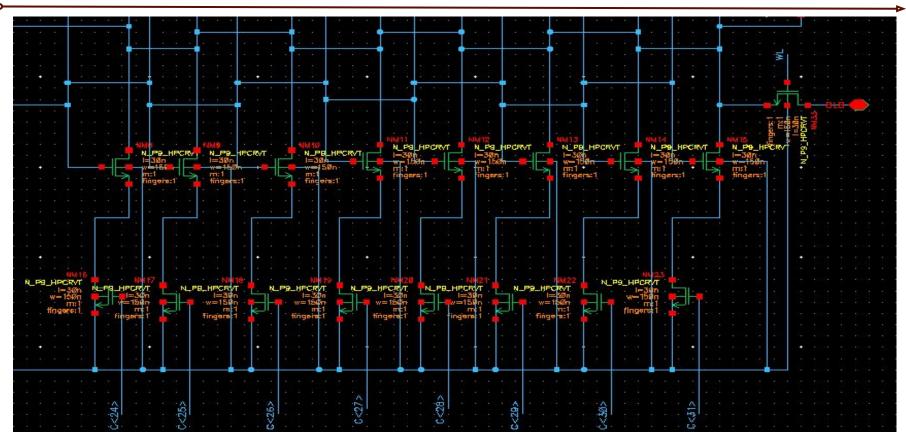

# **Schematic (Top Left of Cell)**

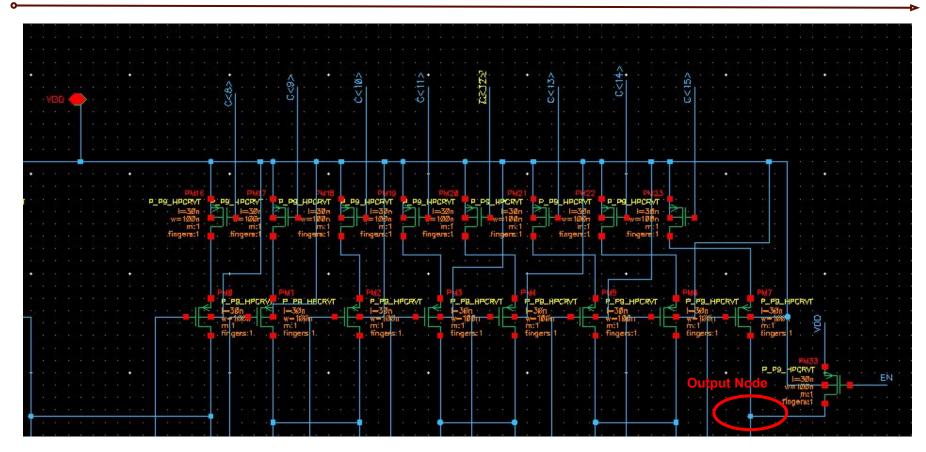

# **Schematic (Top Right of Cell)**

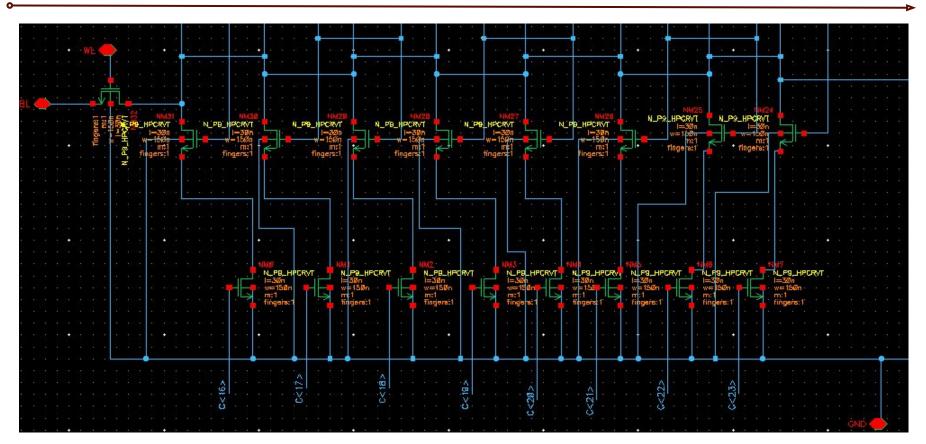

## **Schematic (Bottom Left of Cell)**

## **Schematic (Bottom Right of Cell)**

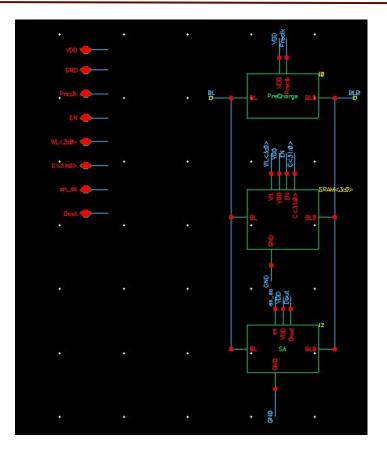

## **Schematic (SRAM-PUF Column)**

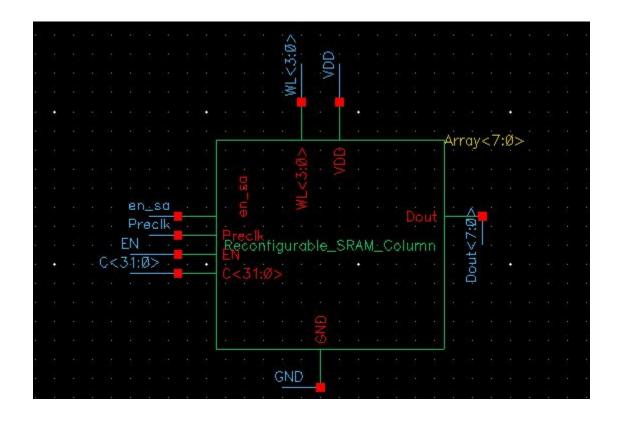

## **Schematic (SRAM-PUF Array)**

## **Circuit Implementation**

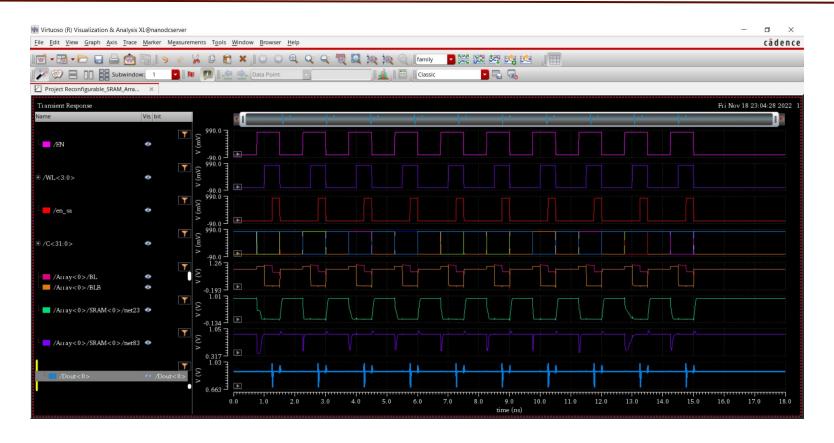

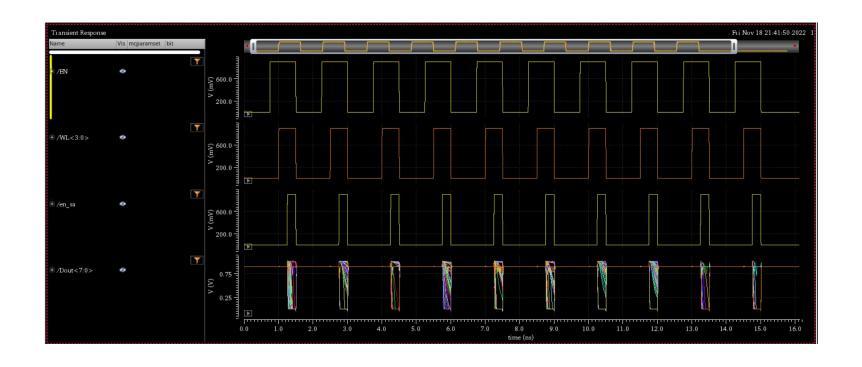

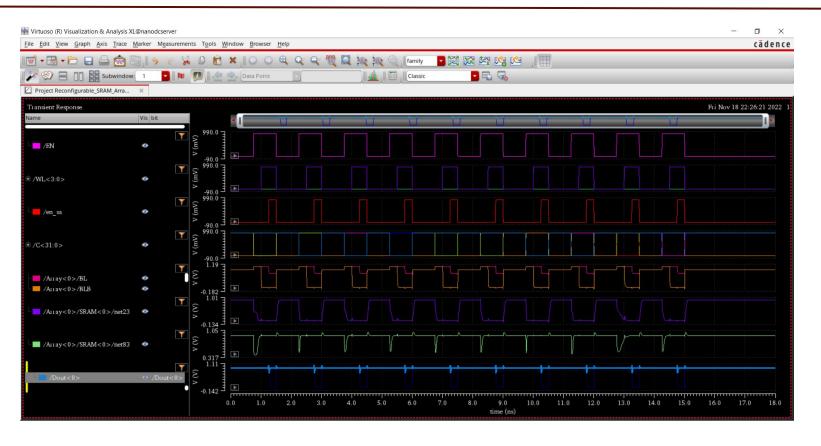

#### **Simulations (ALL WL ON)**

## Simulations (20 Monte Carlo ALL WL ON)

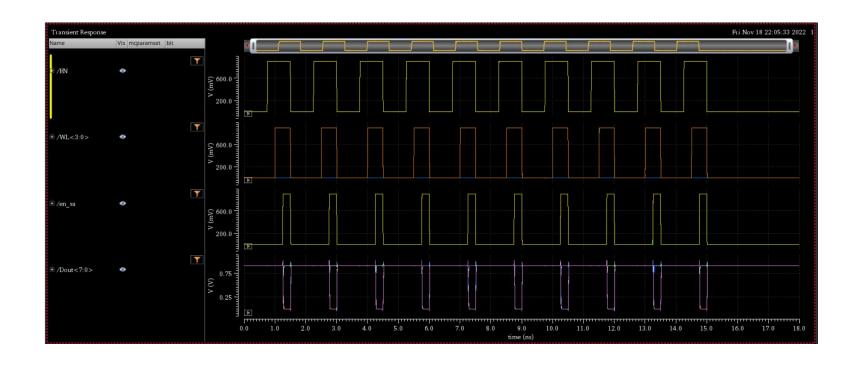

#### Simulations (1 WL ON)

#### Simulations (20 Monte Carlo 1 WL ON)

## Results (Hamming Weight for One Challenge)

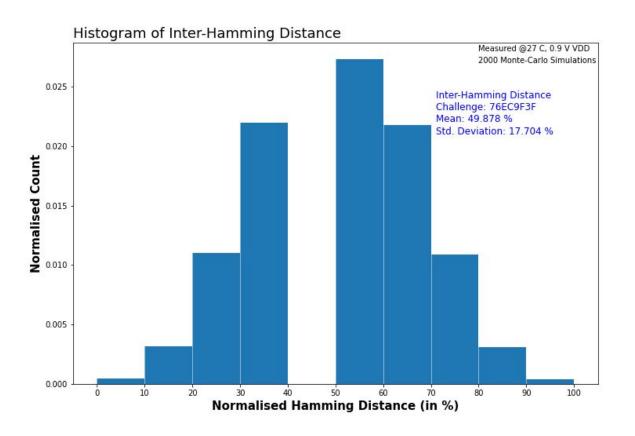

## **Results (Inter-Hamming Distance for One Challenge)**

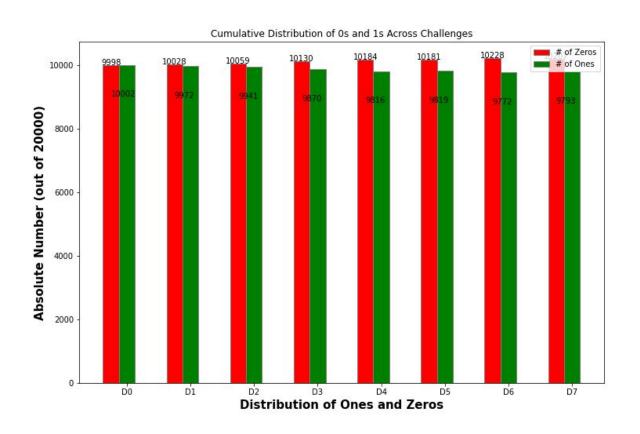

## Results (Hamming Weight with all WL ON)

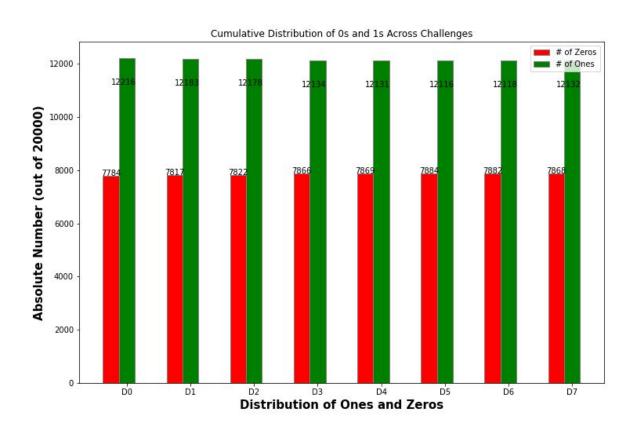

## Results (Hamming Weight with one WL ON)

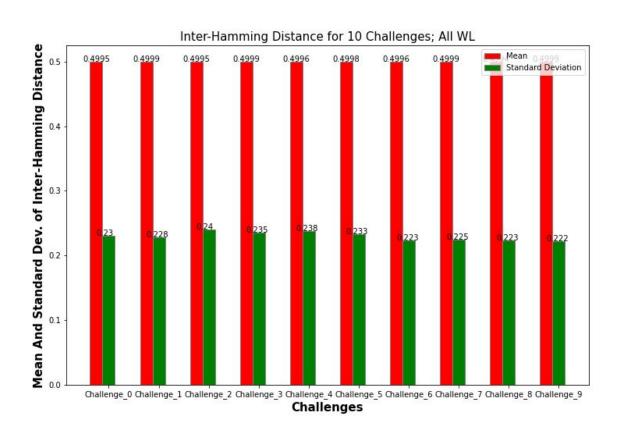

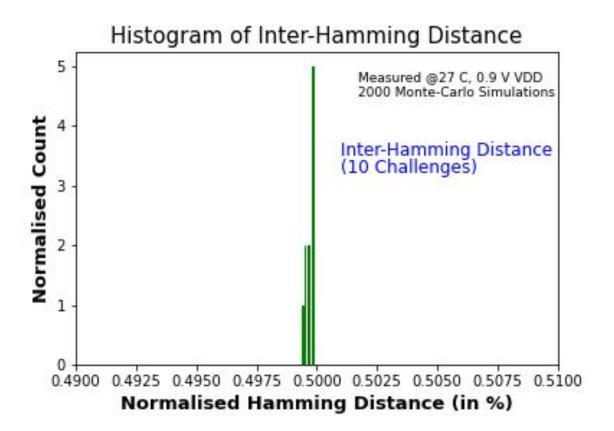

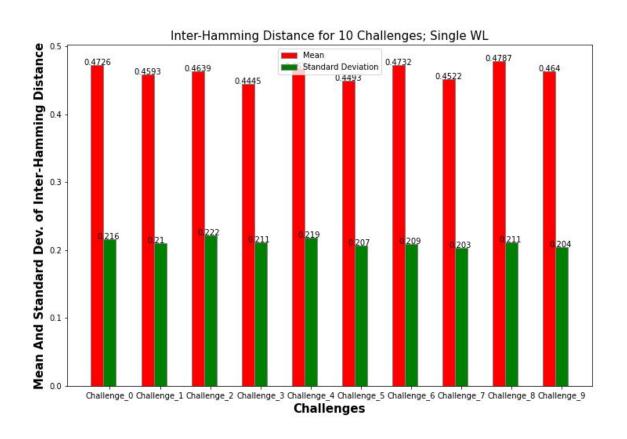

## Results (Inter-Hamming Distance with all WL ON)

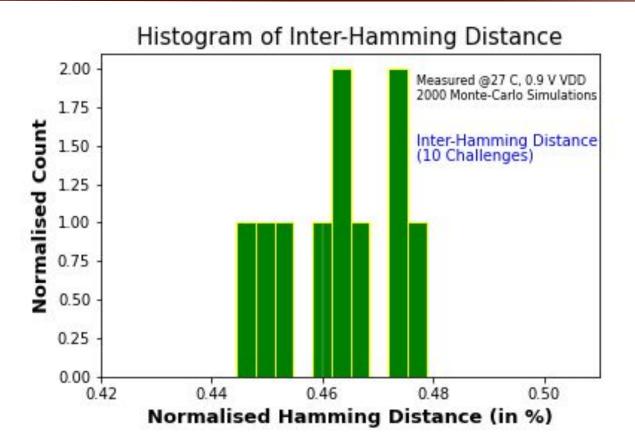

# Results (Inter-Hamming Distance with one WL ON)

## **Results (Inter-Hamming Distance with one WL ON)**

# **Results (NIST Test)**

| TEST                                   | Result |

|----------------------------------------|--------|

| Monobit Test                           | PASS   |

| Frequency Within Block Test            | PASS   |

| Runs Test                              | PASS   |

| Longest Run Ones in a Block Test       | PASS   |

| Binary Matrix Rank Test                | PASS   |

| DFT Test                               | PASS   |

| Non-Overlapping Template Matching Test | PASS   |

# **Results (NIST Test)**

| Overlapping Template Matching Test | FAIL |

|------------------------------------|------|

| Maurers Universal Test             | FAIL |

| Linear Complexity Test             | FAIL |

| Serial Test                        | PASS |

| Approximate Entropy Test           | PASS |

| Cumulative Sums Test               | PASS |

| Random Excursion Test              | FAIL |

| Random Excursion Variant Test      | PASS |

11 Out of 15 Tests Passed!

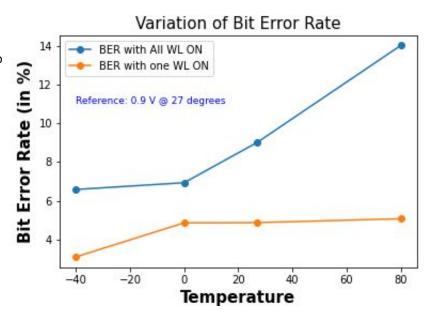

#### Results (BER)

- The worst case bit error was calculated when the supply voltage was increased by 10 %, that is, made 99 mV and temperature was made 80° C.

- Challenge was kept the same when calculating BER.

- The worst case BER in this case is found to be 14.01% when all WL are ON and 5.07% when only one WL is ON! (Reported: 13.7%)

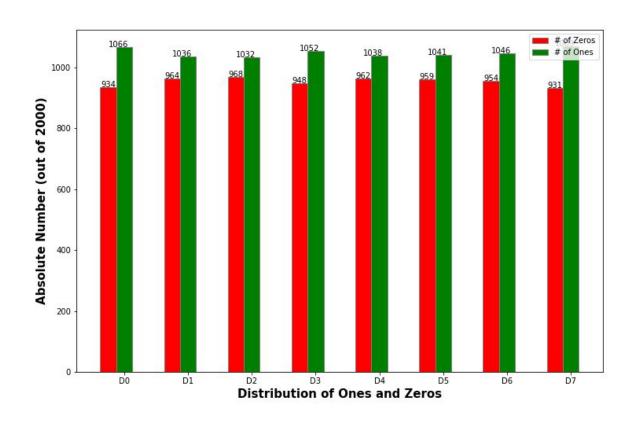

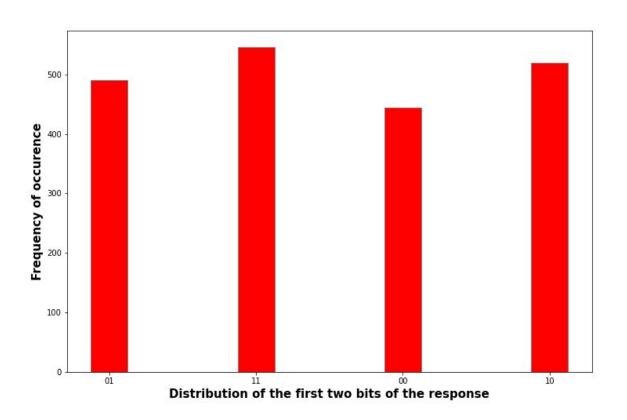

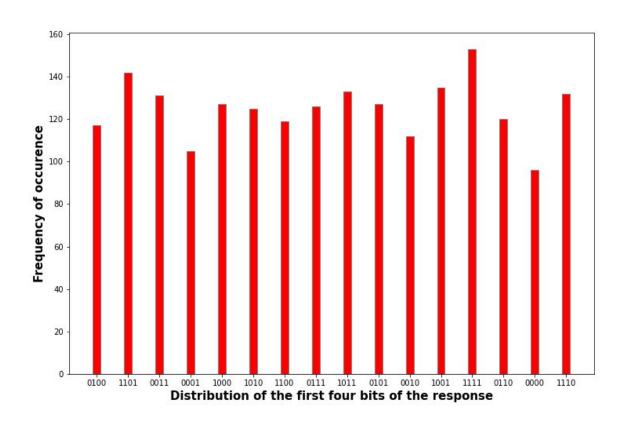

## **Test of Uniformity (Data Visualization)**

## **Test of Uniformity (Data Visualization)**

# Thank You!

#### Any Questions?